ゲート抵抗によるスイッチングノイズ対策

電源におけるスイッチングノイズは、多かれ少なかれ、必ず発生するものです。基本的にはスイッチング周波数が高ければ高いほどノイズが出やすく、低いほどノイズは小さくなる傾向にあります。ただし、スイッチング電源としての機能を満たすためには、電源効率など保った上で、伝導ノイズの規格内に収めるよう設計することが求められます。

スイッチングノイズを低減する方法には様々な方法が存在しますが、今回は「ゲート抵抗によるスイッチングノイズ対策」をお伝えします。

ゲート抵抗値の適正化

一般的にスイッチング素子のゲート抵抗の値を大きくすると、ターンオン・ターンオフ時間が遅くなり、ノイズを抑制することが可能となります。しかしながら、ゲート抵抗の値を大きくすると、ノイズを抑制することができる一方で、反対に効率は低下します。

〇ゲート抵抗の値を小さくすると・・・ノイズ対策↘ 効率改善↗

〇ゲート抵抗の値を大きくすると・・・ノイズ対策↗ 効率改善↘

上記の通り、ノイズ対策と効率改善はトレードオフの関係にあるのです。そのため、ノイズ対策・効率改善の双方と電源用途を鑑みた上で、どの機能を優先すべきか決定し、バランス良く設定することが非常に重要といえます。

ゲート抵抗をスイッチング素子の近くに配置する

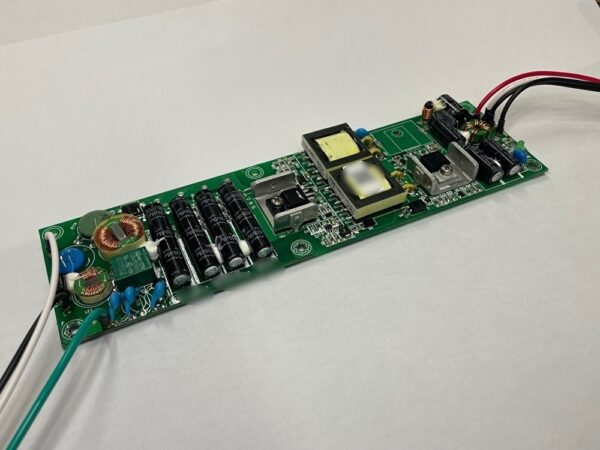

ゲート抵抗におけるノイズ対策としては、ノイズ・効率の双方を鑑みて値を最適化することに加えて、ゲート抵抗の配置位置にも注意を払う必要があります。例えば、スイッチング素子の遠くにゲート抵抗を配置すると、パターンのL成分がノイズとして乗ってしまい、ノイズが増幅してしまう恐れがあります。このような事態を防ぐため、ゲート抵抗はスイッチング素子の近くに配置するようにしましょう。

低ノイズのカスタム電源の開発・設計のことなら、電源開発・設計ソリューションにお任せください!

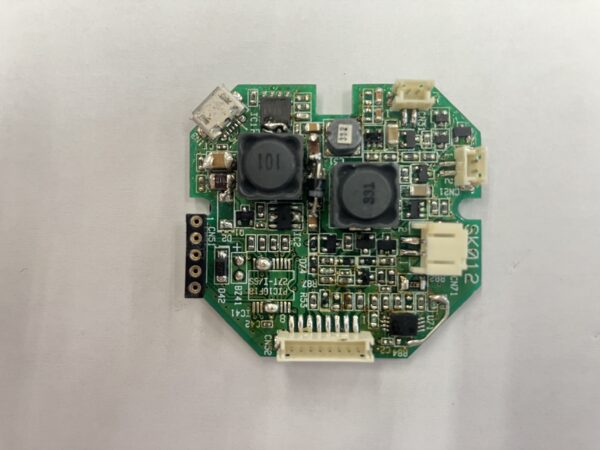

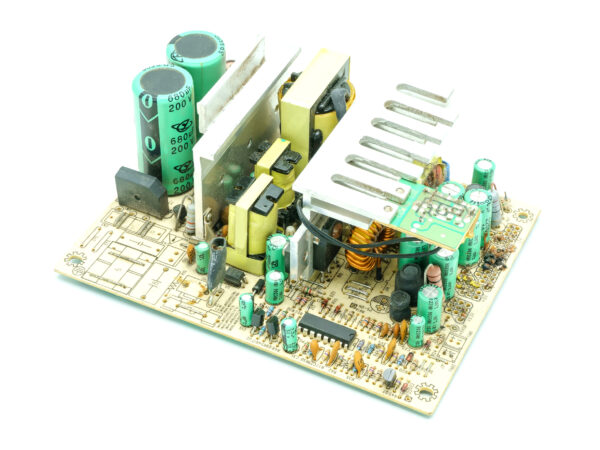

いかがでしたでしょうか。今回は、「ゲート抵抗によるスイッチングノイズ対策」をご紹介しました。電源開発・設計ソリューションを運営するペックでは、小ロットからカスタム電源の開発・設計を承っております。さらには、開発・設計のみならず、製造・評価まで一貫対応しており、これまで幅広いお客様のご要望を実現してまいりました。カスタム電源開発・設計に関するご依頼がございましたら、お気軽にご相談ください。

関連する豆知識

-

【スイッチング電源の設計手順】安全性と品質を保証する実装、評価、最適化

スイッチング電源の安全性と信頼性を確保するためには、保護機能の実装が不可欠です。また、設計した回路が理論通りに機能するかを確認し、さらに性能を向上させるためには、回路図作成、シミュレーション、プリント... -

【スイッチング電源の設計手順】主要部品の選定と基板設計のポイント

スイッチング電源の設計において、要求仕様の確認と回路方式の選定は設計の方向性を決定する重要なステップです。本コラムでは、電源の効率、サイズ、コスト、そしてEMI特性に大きく影響するスイッチング周波数の... -

【スイッチング電源の設計手順】安定動作とノイズ対策の要点

スイッチング電源の設計は、単に部品を選んで回路を組むだけではありません。電源が安定して動作し、かつ外部機器に悪影響を与えず、自身もノイズによる誤動作を起こさないようにするには、フィードバック回路設計と... -

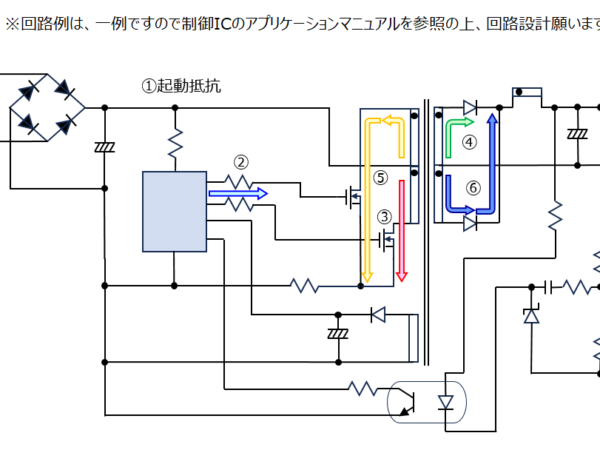

位相シフトフルブリッジ方式(フルブリッジ方式)の概略動作と特性

当記事では、絶縁タイプの位相シフトフルブリッジ方式(フルブリッジ方式)の概略動作と特性について解説します。 位相シフトフルブリッジ方式(フルブリッジ方式)の概略動作と特性 他の方式同様に制御用ICが起... -

【スイッチング電源の設計手順】要求仕様の確認から回路方式選定

スイッチング電源の設計手順は、仕様に合わせて電源回路方式の選定、主要部品の最適化、保護回路の設定と段階的に進める必要があります。仕様に応じた回路選定を間違えると、言われている効率まで上がらないであった... -

プッシュプル方式の概略動作と特性

当記事では、絶縁タイプの回路方式:プッシュプル方式の概略動作と特性の概略動作と特性について解説します。 プッシュプル方式の概略動作と特性の回路動作 プッシュプル回路方式においては、DC(直流)出力のみ...

一覧はこちら