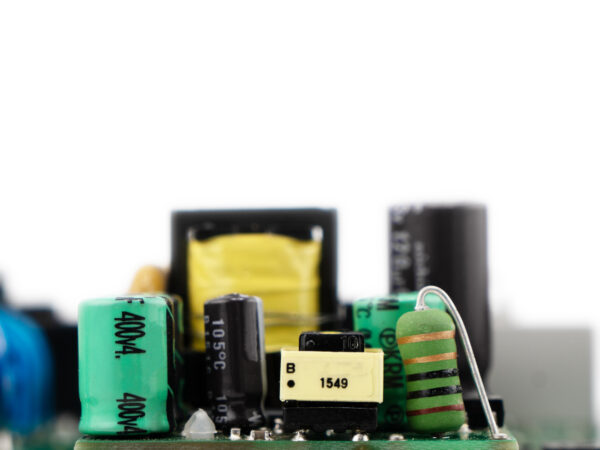

カスタム電源の小型化を実現する設計ポイント

電子機器の高性能化に伴い、スイッチング電源の小型化の必要性が高まっています。本記事では、スイッチング動作の高周波化や部品選定などといったスイッチング電源を小型化するためのポイントについてご紹介します。

カスタム電源の小型化を実現する設計ポイント

ポイント①:サイズの小さいICを優先的に選定する

電源基板の小型化を実現するためには、まずICの選定が重要になります。ICが小さければ実装面積を削減でき、基板全体を小型化することができます。しかし単にサイズだけで判断するのではなく、必要な機能を十分に満たしているかを確認することが前提となります。

最近の電源ICは高集積化が進んでおり、スイッチング素子や保護回路を内蔵したタイプも多く登場しています。これにより外付け部品の点数を減らし、小型化と同時に設計の簡素化も可能となります。

ポイント②:スイッチング動作の高周波化により、部品サイズを抑制する

スイッチング電源では、インダクタやコンデンサといった部品のサイズが周波数に依存するため、発振周波数を高めることで小型化を図る方法があります。これにより、インダクタやコンデンサ等の物理サイズが小さく済むため、全体を小型化することが可能です。

例えば、高周波化により電解コンデンサを用いる必要がなくなり、積層セラミックコンデンサに置き換えることになり、高さ方向の制約を緩和でき、より薄型化された電源回路の構成が可能になります。

ただし、スイッチング動作の高周波化にはいくつかの弊害が伴います。

発熱・損失の増大

高周波になると、体積あたりのW数が増加し、発熱量が高まります。その結果、効率が低下し、損失が増大するリスクがあるため、熱対策を考慮する必要があります。

ノイズの増大

高周波スイッチングによってノイズが発生しやすくなるため、ノイズフィルタやスナバ回路の使用などの対策が必要になります。

ポイント③:小型化を最優先したレイアウト設計とする

本当に小型化したい場合は、「物理的な最小化」を最優先し、ノイズ対策や熱対策のための余裕を削り取ることも重要です。具体的な施策例は下記の通りです。

部品の超近接配置

電源ICと、その動作に必須な入出力コンデンサやインダクタを、物理的に接触するほど密集して配置します。特にスイッチング・ホット・ループ(スイッチング電流が流れる経路)は、最短かつ最小面積になるように部品配置と配線を行います。これにより、寄生インダクタンス(ESL)を最小化し、効率とEMI(電磁干渉)抑制にも結果的に貢献します。

立体的な部品配置

また、部品の超近接配置のみならず、立体的な部品配置とすることも重要です。具体的には、SMD部品の上に、リードを伸ばしたDIP部品を設置することで、立体的な構造とするのです。ただし、実装時の難易度が上がるため、注意が必要です。

配線長の極小化

電源ラインやグランドラインといった大電流パスの配線長を極限まで短く、太く引き回し、電力損失と寄生抵抗を抑えます。

多層基板の活用

部品を両面に実装する、または配線を立体的に引き回すために層数を増やす(例:4層、6層)ことで、平面的な面積を最小化します。電源層やグランド層を適切に配置することで、ノイズ抑制の役割も担わせます。

電源回路の小型化は当社にお任せください

今回は、小型化を実現する電源回路の設計ポイントについてご紹介しました。電源開発設計ソリューションを運営するペック株式会社では、お客様の仕様やご要望に合わせたカスタム電源の製造の豊富な実績がございます。お困りの方はお気軽に当社にご連絡ください。

関連する豆知識

-

防水・防塵(IP規格)に対応した電源筐体設計

屋外設備や産業用ロボット、工作機械など過酷な環境下で使用される電子機器において、電源ユニットの信頼性を担保する「防水・防塵設計」は極めて重要です。IP規格への適合は、単に水の浸入を防ぐだけでなく、製品... -

カスタム電源開発・設計における冷却方式の選定ポイント

カスタム電源の仕様検討において、「静かな自然空冷にしたい」「小型化のためにファンを付けたい」といったご要望は頻繁に挙がります。しかし、その選択は単なる「好み」や「機能の有無」だけで決めてよいものではあ... -

カスタム電源におけるフェイルセーフを実現する保護回路の動作特性

カスタム電源の設計では、効率・コスト・サイズといった基本仕様と並び、フェイルセーフ設計は欠かせない要素です。特に産業機器、通信機器、医療機器など、突然な停止や誤動作が重大な影響を及ぼすシステムでは、異... -

セミカスタム電源を活用すべきケースとは?

製品開発において、電源は重要な基幹部品です。しかし、開発現場では「標準電源では要求仕様を満たせないが、フルカスタムで新規開発するほど複雑な要件ではない」という状況に直面することがあります。このような状... -

高難度!カスタム電源の不具合解析事例をご紹介!

当記事では、電源開発・設計ソリューションを運営するペック株式会社が対応したカスタム電源の不具合解析の具体的な事例をご紹介します。不具合解析をご検討中の方は、是非ご参考ください。 不具合症状 とあるメー... -

短納期で実現するカスタム電源開発の手法

製品性能を最大限に引き出すには、仕様に合ったカスタム電源が欠かせません。しかし「カスタム」と聞くと、長い開発期間や高額なコストを思い浮かべてしまう方も多いのではないでしょうか。特に市場投入までのスピー...

一覧はこちら